资源简介

参考《16位5级流水无cache实验CPU课程设计实验要求》文档及其VHDL代码,在理解其思想和方法的基础上,将其改造成8位的5级流水无cache的实验CPU,包括对指令系统、数据通路、各流水段模块、内存模块等方面的改造。利用VHDL语言编程实现,并在TEC-CA平台上进行仿真测试。为方便起见,后续16位5级流水无cache实验CPU简记为ExpCPU-16,而8位的则记为ExpCPU-8。

对于内存模块的改造,参考《计算机组成原理》课程综合实验的方法,独立设计一块8位的RAM。

(1)利用TEC-CA平台上的16位RAM来存放8位的指令和数据;

(2)实现一条JRS指令,以便在符号标志位S=1时跳转。需要改写ID段的控制信息,并改写IF段;

(3)实现一条CMPJ DR,SR,offset指令,当比较的两个数相等时,跳转到目标地址PC+1+offset;

(4)可以探索从外部输入指令,而不是初始化时将指令“写死”在RAM中;

(5)此5段流水模块之间,并没有明显地加上流水寄存器,可以考虑在不同模块间加上流水寄存器;

(6)探索5段流水带cache的CPU的设计。

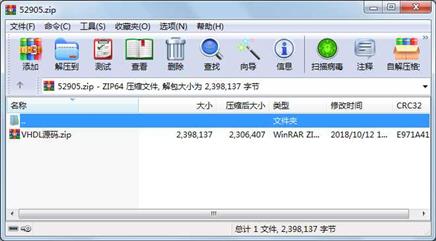

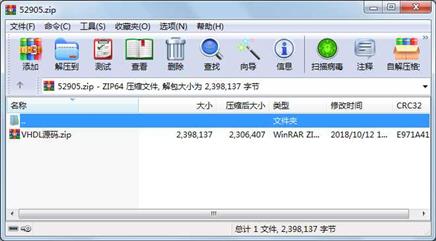

代码片段和文件信息

属性 大小 日期 时间 名称

----------- --------- ---------- ----- ----

文件 2398137 2018-10-12 16:37 VHDL源码.zip

----------- --------- ---------- ----- ----

文件 2398137 2018-10-12 16:37 VHDL源码.zip

相关资源

- 计组实验(ALU的设计)

- 湖南大学计算机组成与原理实验已完

- 华南农业大学-《数据库系统》实验报

- 计算机组成原理实验报告全部实验.

- 广工计算机组成原理实验报告.docx

- 单周期CPU设计

- 西南交大计算机组成原理综合实验

- 西南交大计组实验1-8.zip

- 杭电计组实验1-7(新板子).zip

- 操作系统期末考卷

- 算法设计与分析试卷

- 网络编程期末试卷华南农业大学2011含

- alu-EduCoder-3-29.circ

- 华南农业大学2018人工智能复习题

- 华南农业大学锐捷客户端forMac

- 计组实验报告

- 华南农业大学数据结构上机题目答案

- 华南农业大学数据结构实验答案(包

- 华南农业大学汇编课程设计学生信息

- 华南农业大学人工智能期末复习

- 华农网络编程socket通信

- 微程序控制的访存系统设计

- 北航计组实验代码三p4--Verilog单周期

- 北航计组实验代码和电路二Logisim单周

- 北航计组实验二p3--Logisim单周期

- 北航计组实验代码、电路一

- ALU Verilog计组实验文件

- MIPS多周期CPU设计

- 华南农业大学数电实验参考答案

- 华南农业大学计算机组成原理综合性

川公网安备 51152502000135号

川公网安备 51152502000135号

评论

共有 条评论