-

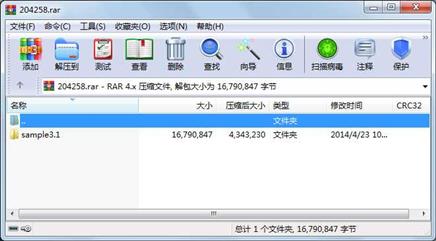

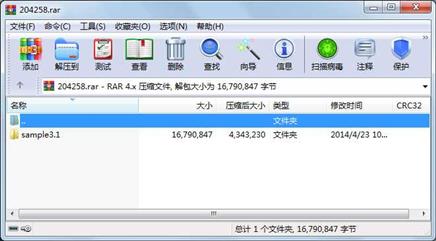

大小: 4.18MB文件类型: .rar金币: 2下载: 0 次发布日期: 2023-10-22

- 语言: 其他

- 标签: Verilog PCM1750U/P

资源简介

使用ISE14.3编译环境。FPGA采用的是Spartan6系列,板子是Nexys3。

代码片段和文件信息

/**********************************************************************/

/* ____ ____ */

/* / /\/ / */

/* /___/ \ / */

/* \ \ \/ */

/* \ \ Copyright (c) 2003-2009 Xilinx Inc. */

/* / / All Right Reserved. */

/* /---/ /\ */

/* \ \ / \ */

/* \___\/\___\ */

/***********************************************************************/

/* This file is designed for use with ISim build 0x8ef4fb42 */

#define XSI_HIDE_SYMBOL_SPEC true

#include “xsi.h“

#include

#ifdef __GNUC__

#include

#else

#include

#define alloca _alloca

#endif

static int ng0[] = {0 0 0 0};

static int ng1[] = {0 0};

static const char *ng2 = “ Warning : Input clock period of %1.3f ns on the %s port of instance %m exceeds allowed value of %1.3f ns at time %1.3f ns.“;

static void Initial_1176_0(char *t0)

{

char *t1;

char *t2;

LAB0:

LAB2: t1 = ((char*)((ng0)));

t2 = (t0 + 1080);

xsi_vlogvar_assign_value(t2 t1 0 0 64);

t1 = ((char*)((ng0)));

t2 = (t0 + 1172);

xsi_vlogvar_assign_value(t2 t1 0 0 64);

LAB1: return;

}

static void Always_1181_1(char *t0)

{

char t4[16];

char t7[16];

char t16[8];

char t43[8];

char t49[8];

char t52[8];

char *t1;

char *t2;

char *t3;

char *t5;

char *t6;

char *t8;

unsigned int t9;

unsigned int t10;

unsigned int t11;

unsigned int t12;

unsigned int t13;

char *t14;

char *t15;

char *t17;

char *t18;

unsigned int t19;

unsigned int t20;

unsigned int t21;

unsigned int t22;

unsigned int t23;

unsigned int t24;

unsigned int t25;

unsigned int t26;

unsigned int t27;

unsigned int t28;

unsigned int t29;

unsigned int t30;

char *t31;

char *t32;

unsigned int t33;

unsigned int t34;

unsigned int t35;

unsigned int t36;

unsigned int t37;

char *t38;

char *t39;

char *t40;

double t41;

double t42;

char *t44;

char *t45;

char *t46;

double t47;

double t48;

double t50;

double t51;

LAB0: t1 = (t0 + 1840U);

t2 = *((char **)t1);

if (t2 == 0)

goto LAB2;

LAB3: goto *t2;

LAB2: t2 = (t0 + 2036);

*((int *)t2) = 1;

t3 = (t0 + 1868);

*((char **)t3) = t2;

*((char **)t1) = &&LAB4;

LAB1: return;

LAB4:

LAB5: t5 = xsi_vlog_time(t4 1.0000000000000000 1.0000000000000000);

t6 = (t0 + 1080);

xsi_vl属性 大小 日期 时间 名称

----------- --------- ---------- ----- ----

文件 197 2014-04-22 21:16 sample3.1\AAA此文件夹说明.txt

文件 245 2014-04-22 21:16 sample3.1\ADprocess.cmd_log

文件 222 2014-04-22 21:16 sample3.1\ADprocess.tfi

文件 6364 2014-04-22 21:16 sample3.1\chipscope.cdc

文件 7219 2014-04-22 21:16 sample3.1\default_waveform.pdf

文件 239 2014-04-22 21:16 sample3.1\Display.cmd_log

文件 171 2014-04-22 21:16 sample3.1\Display.tfi

文件 1931 2014-04-22 21:16 sample3.1\fuse.log

文件 594 2014-04-22 21:16 sample3.1\fuse.xmsgs

文件 268 2014-04-22 21:16 sample3.1\fuseRelaunch.cmd

文件 902 2014-04-22 21:16 sample3.1\ge_12288kHz.v

文件 1477 2014-04-22 21:16 sample3.1\impact.xsl

文件 256 2014-04-22 21:16 sample3.1\impact_impact.xwbt

文件 302354 2014-04-22 21:16 sample3.1\ipcore_dir\ConverToCommon\doc\mult_gen_ds255.pdf

文件 7412 2014-04-22 21:16 sample3.1\ipcore_dir\ConverToCommon\doc\mult_gen_v11_2_readme.txt

文件 8072 2014-04-22 21:16 sample3.1\ipcore_dir\ConverToCommon\doc\mult_gen_v11_2_vinfo.html

文件 431 2014-04-22 21:16 sample3.1\ipcore_dir\ConverToCommon.asy

文件 1388 2014-04-22 21:16 sample3.1\ipcore_dir\ConverToCommon.gise

文件 100617 2014-04-22 21:16 sample3.1\ipcore_dir\ConverToCommon.ngc

文件 1292 2014-04-22 21:16 sample3.1\ipcore_dir\ConverToCommon.sym

文件 128503 2014-04-22 21:16 sample3.1\ipcore_dir\ConverToCommon.v

文件 3788 2014-04-22 21:16 sample3.1\ipcore_dir\ConverToCommon.veo

文件 1912 2014-04-22 21:16 sample3.1\ipcore_dir\ConverToCommon.xco

文件 4931 2014-04-22 21:16 sample3.1\ipcore_dir\ConverToCommon.xise

文件 411 2014-04-22 21:16 sample3.1\ipcore_dir\ConverToCommon_flist.txt

文件 3337 2014-04-22 21:16 sample3.1\ipcore_dir\ConverToCommon_xmdf.tcl

文件 238 2014-04-22 21:16 sample3.1\ipcore_dir\coregen.cgp

文件 3239 2014-04-22 21:16 sample3.1\ipcore_dir\coregen.log

文件 1257 2014-04-22 21:16 sample3.1\ipcore_dir\create_ConverToCommon.tcl

文件 1256 2014-04-22 21:16 sample3.1\ipcore_dir\create_geClk5M.tcl

............此处省略529个文件信息

- 上一篇:网络调试助手-全平台

- 下一篇:海康sip信令抓包

相关资源

- 基于MIPS指令集的32位CPU设计与Verilog语

- Verilog FPGA UART串口控制器

- gmsk调制在FPGA上实现

- 一个简单的verilog编写的DMA IP CORE,和

- 硬件课程设计—流水灯(quartus软件

- Verilog按键代码

- verilog的PCI源代码,非常详细,顶层模

- CPLD Verilog数字密码锁 源码

- verilog 实现任意分频方法

- DE2模拟的交通红绿灯

- SPI Master 的Verilog源代码

- 基于VGA的Flappy Bird的Verilog实现(源码

- 数字钟

- Verilog的135个经典设计

- verilog 4×4矩阵键盘

- Quartus EDA交通灯控制电路的设计实训报

- FPGA按键消抖

- 用Verilog语言写的CPLD和MCU通讯的SPI接口

- ARM9指令cache的verilog代码

- ddr_verilog

- FPGA实现单极性SPWM调制

- uart_tx.zip

- 基于Verilog的cordic反正切FPGA例程

- SystemVerilog验证测试平台编写指南(中

- 基于Verilog的交通灯设计EDA课程设计

- 数字信号处理的FPGA实现Verilog源码

- verilog硬件描述语言程序设计与实践教

- Ultraedit环境下配置verilog语法高亮的字

- 8 位cpu的verilog

- 中值滤波算法Quartus实现

川公网安备 51152502000135号

川公网安备 51152502000135号

评论

共有 条评论