-

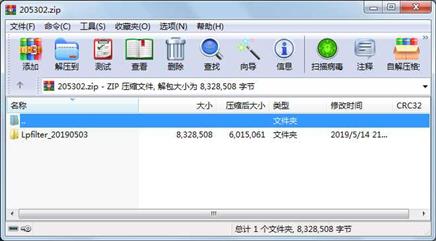

大小: 5.83MB文件类型: .zip金币: 2下载: 0 次发布日期: 2023-10-22

- 语言: 其他

- 标签: PLL FLL Verilog Loop_Filter

资源简介

环路滤波器是通信信号调制解调中最重要的一个部分,环路滤波器设计的好坏将直接影响到接收机的性能指标,二阶锁频辅助三阶锁相环路滤波器可以稳定跟踪具有加加速度的信号源,是现代通信中非常实用的技术,本文中详细编写了单载波信号产生模块、信道噪声模块、数字正交下变频模块、鉴频鉴相模块、环路滤波器模块,并包含了完整的testbench模块,对于初学者非常有用。

代码片段和文件信息

% Altera NCO version 13.1

% function [sc] = Nco_Signal_model(phi_inc_iphase_mod_ifreq_mod_i)

% input : phi_inc_i : phase increment input (required)

% phase_mod_i : phase modulation input(optional)

% freq_mod_i : frequency modulation input(optional)

% output : s : sine wave output

% c : cosine wave output

function [sc] = Nco_Signal_model(phi_inc_iphase_mod_ifreq_mod_i)

addpath d:/altera/ip/altera/nco/lib/ip_toolbench/../;

if(nargin==0)

fprintf(‘Error using Nco_Signal_model : Not enough input arguments\n‘);

else

N=length(phi_inc_i);

end

if(nargin==1)

phase_mod_i=zeros(1N);

freq_mod_i=zeros(1N);

elseif(nargin==2)

if(length(phase_mod_i)~=N)

fprintf(‘Error using Nco_Signal_model : input vector length mismatch\n‘);

else

freq_mod_i=zeros(1N);

end

elseif(nargin==3)

if((length(phase_mod_i)~=N)|length(freq_mod_i)~=N)

fprintf(‘Error using Nco_Signal_model : input vector length mismatch\n‘);

end

else

fprintf(‘Error using Nco_Signal_model : Incorrect number of input arguments\n‘);

end

N=length(phi_inc_i);

numch = 1.0;

apr = 32.0;

apri = 12.0;

mpr = 12.0;

aprp = 16.0;

aprf = 32.0;

dpri = 6.0;

arch = 0.0;

wantFmod = 1.0;

wantPmod = 1.0;

dual = 1.0;

[sc] = Sncomodel(phi_inc_iphase_mod_ifreq_mod_iwantFmodwantPmodnumchaprmprapriaprpaprfdpriarchdualN);

属性 大小 日期 时间 名称

----------- --------- ---------- ----- ----

目录 0 2019-05-14 21:47 Lpfilter_20190503\

文件 1674 2019-05-09 21:47 Lpfilter_20190503\Cordic12b_Atan.v

文件 1567 2019-05-09 21:37 Lpfilter_20190503\Cordic12b_Atan.v.bak

文件 1674 2019-05-09 21:47 Lpfilter_20190503\Cordic24b_Atan.v

文件 1674 2019-05-09 21:46 Lpfilter_20190503\Cordic24b_Atan.v.bak

目录 0 2019-05-14 21:47 Lpfilter_20190503\db\

文件 1840 2019-05-09 22:10 Lpfilter_20190503\db\add_sub_55h.tdf

文件 1840 2019-05-09 22:10 Lpfilter_20190503\db\add_sub_75h.tdf

文件 1769 2019-05-09 22:10 Lpfilter_20190503\db\add_sub_s1i.tdf

文件 1767 2019-05-09 22:10 Lpfilter_20190503\db\add_sub_sqh.tdf

文件 12718 2019-05-09 22:10 Lpfilter_20190503\db\altsyncram_0hj1.tdf

文件 12845 2019-05-14 21:19 Lpfilter_20190503\db\altsyncram_99k1.tdf

文件 22159 2019-05-14 21:22 Lpfilter_20190503\db\altsyncram_e6k2.tdf

文件 3056 2019-05-14 21:22 Lpfilter_20190503\db\altsyncram_f6m1.tdf

文件 12806 2019-05-14 21:07 Lpfilter_20190503\db\altsyncram_nvj1.tdf

文件 12718 2019-05-09 22:10 Lpfilter_20190503\db\altsyncram_rgj1.tdf

文件 3531 2019-05-09 22:10 Lpfilter_20190503\db\cntr_loi.tdf

文件 5672 2019-05-09 22:10 Lpfilter_20190503\db\fpga_top.(0).cnf.cdb

文件 2253 2019-05-09 22:10 Lpfilter_20190503\db\fpga_top.(0).cnf.hdb

文件 4609 2019-05-14 21:28 Lpfilter_20190503\db\fpga_top.(1).cnf.cdb

文件 1754 2019-05-14 21:28 Lpfilter_20190503\db\fpga_top.(1).cnf.hdb

文件 2170 2019-05-09 22:10 Lpfilter_20190503\db\fpga_top.(10).cnf.cdb

文件 676 2019-05-09 22:10 Lpfilter_20190503\db\fpga_top.(10).cnf.hdb

文件 2903 2019-05-09 22:10 Lpfilter_20190503\db\fpga_top.(11).cnf.cdb

文件 920 2019-05-09 22:10 Lpfilter_20190503\db\fpga_top.(11).cnf.hdb

文件 2139 2019-05-09 22:10 Lpfilter_20190503\db\fpga_top.(12).cnf.cdb

文件 993 2019-05-09 22:10 Lpfilter_20190503\db\fpga_top.(12).cnf.hdb

文件 2857 2019-05-09 22:10 Lpfilter_20190503\db\fpga_top.(13).cnf.cdb

文件 1390 2019-05-09 22:10 Lpfilter_20190503\db\fpga_top.(13).cnf.hdb

文件 1712 2019-05-09 22:10 Lpfilter_20190503\db\fpga_top.(14).cnf.cdb

文件 674 2019-05-09 22:10 Lpfilter_20190503\db\fpga_top.(14).cnf.hdb

............此处省略436个文件信息

相关资源

- 基于MIPS指令集的32位CPU设计与Verilog语

- Verilog FPGA UART串口控制器

- gmsk调制在FPGA上实现

- 一个简单的verilog编写的DMA IP CORE,和

- 硬件课程设计—流水灯(quartus软件

- Verilog按键代码

- verilog的PCI源代码,非常详细,顶层模

- CPLD Verilog数字密码锁 源码

- verilog 实现任意分频方法

- DE2模拟的交通红绿灯

- SPI Master 的Verilog源代码

- 基于VGA的Flappy Bird的Verilog实现(源码

- 数字钟

- Verilog的135个经典设计

- verilog 4×4矩阵键盘

- Quartus EDA交通灯控制电路的设计实训报

- FPGA按键消抖

- PLL回路滤波器设计的调整指南

- PLL回路滤波器设计调整指南及使用案

- 翻译的美国大学经典参考书,Roland

- 玩转Altera FPGA:基于PLL分频计数的LE

- PLL原理讲义 一个典型的锁相环PLL系统

- 锁相环PLL偏离整数通道的频率点杂散

- PLL例化配置与LED之PLL的IP核配置

- 双二阶广义积分器SOGI软件锁相(基于

- 用Verilog语言写的CPLD和MCU通讯的SPI接口

- ARM9指令cache的verilog代码

- ddr_verilog

- 宽频带数字锁相环的设计及基于FPGA的

- PLL和DLL:都是锁相环,区别在哪里?

川公网安备 51152502000135号

川公网安备 51152502000135号

评论

共有 条评论